FeSens 在 GitHub 公开了一项 CPU 自动优化实验:一个自治研发循环在 9 小时 51 分钟内,对一颗 SystemVerilog 编写的 5 级顺序 RV32IM 核提出、实现并测试 73 个微架构假设,最终接受 10 个改动。终态指标为 2.91 CoreMark/MHz、577 iter/s、199 MHz Fmax、5,944 LUT4,较锁定基线约提升 92%。

这条新闻容易被误读成“AI 自动设计 CPU”。更准确的说法是,AI 在一个边界清楚、验证链很硬的沙箱里,做了一轮自动化微架构调参和筛选。它的价值不在 agent loop 多聪明,而在失败样本能被及时挡住。

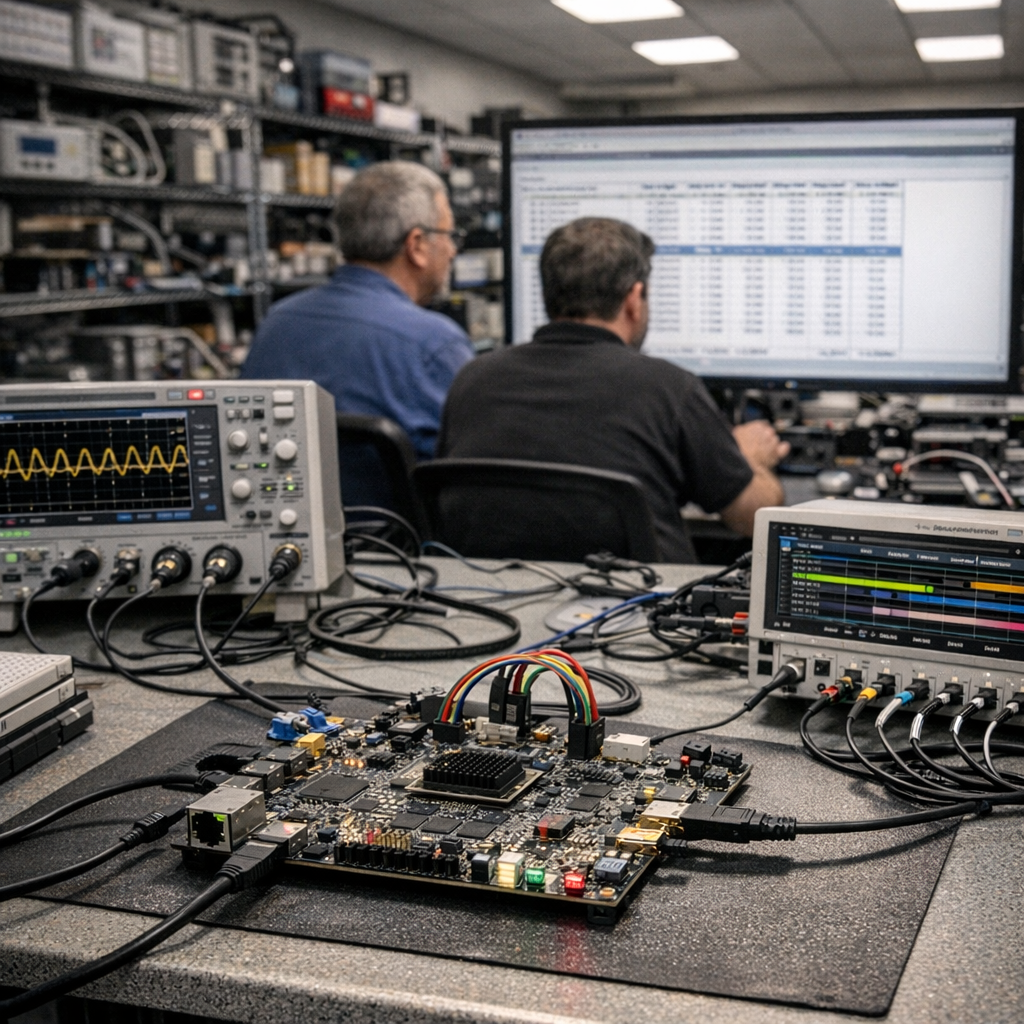

FeSens 的实验对象是一颗很朴素的 RV32IM 核

实验起点不是高端乱序核,而是一颗教材式 5 级顺序流水线 CPU:无缓存、无分支预测、无多发射。agent 每轮提出 YAML 假设,再由实现 agent 修改 rtl/ 下代码,最后进入评测门。

评测链比“跑通 benchmark”严格得多,包括 riscv-formal、Verilator cosim、3-seed nextpnr 布局布线、CoreMark CRC 校验和路径沙箱。路径沙箱限制 agent 只能改指定目录,避免它通过改测试、改评估脚本来“刷分”。

| 项目 | 基线 | 终态 | 判断 |

|---|---|---|---|

| CoreMark/MHz | 2.23 | 2.91 | 架构效率有提升 |

| CoreMark iter/s | 301 | 577 | 总性能约 +92% |

| Fmax | 135 MHz | 199 MHz | 综合后频率明显提高 |

| LUT4 | 9,880 | 5,944 | 面积反而下降 |

被接受的 10 项改动包括后向分支预测、直接跳转预测、冷路径多周期 DIV/REM、单深度 store retirement slot、I-Fetch replay predictor、hot/cold ALU opcode split 等。最关键的一步是把 DIV/REM 从单周期 ALU 路径中移出,既提高频率,也大幅降低 LUT。

63 个失败样本,才是这项实验最该看的部分

73 个假设里,只有 10 个被接受;50 个回归,9 个 broken,4 个布局布线失败。这个比例说明,自动研发循环不是稳定地产生正确设计,而是在大量试错中靠验证器筛掉坏结果。

原文给出的几个失败例子很说明问题。同一个“移出 DIV/REM”思路第一次实现时 cosim 就坏了,两个小时后换一种实现才成为性能突破。还有假设试图在允许范围外新增测试辅助文件,被路径沙箱拦下。更危险的是,一个 JALR 预测相关改动曾让性能下降 73%,如果没有与当前基线比较,前面所有收益会被一次合并抹掉。

这对 AI 工程团队和芯片、编译器、基础设施团队的启发很直接:预算不该只投在更复杂的 planner、更多 agent 或更漂亮的工作流上。能写清楚“什么叫正确”的验证器,才决定自动化研发能不能进生产链路。

对比 VexRiscv 要谨慎,商业含义也要收窄

FeSens 作者把结果与 VexRiscv published full no cache 指标做了对照,称在 CoreMark iter/s 上高出约 56%,且 LUT 更少。但这不是严格同条件全面胜出。它发生在单一 FPGA、单一 workload、相近但仍需审慎看待的方法学里。

VexRiscv 是开源 RISC-V 生态里长期被使用的可配置 CPU 项目,指标积累来自多年工程迭代。FeSens 这次更像证明:在明确目标函数、固定硬件平台、强验证链保护下,agent 可以快速扫出人类工程师未必会优先尝试的局部优化。它还没有证明这些优化能迁移到 Embench、真实嵌入式负载,或不同 FPGA/ASIC 工艺。

受影响最大的是正在做自动化研发平台的团队。若业务对象像 CPU ISA、编译器差分测试、账务流水不变量那样可被形式化描述,agent loop 有机会变成高效实验机器;若规则散落在老工程师脑中、文档和线上事故复盘里,它只会更快地产生看似正确的错误。接下来最该观察的不是下一轮 agent 换了什么模型,而是这些改动在 Embench 和更多硬件目标上能留下多少。