I/O 规划中的挑战,以下为 Altera Interface Planner 的目标环境>

目标 Quartus Prime:Quartus Prime 专业版,目标 FPGA:Quartus Prime 专业版支持的 FPGA 系列,在现代 FPGA 中创建 I/O 分配主要面临的挑战包括:日益复杂的 I/O 标准和 FPGA I/O 结构 (准确设计引脚布局需要更多指导步骤)、PCB 开发与 FPGA 设计同时进行 (或稍早) 和在设计周期早期验证引脚分配。为了应对这些挑战,Quartus Prime 提供了 Pin Planner 和 I/O Assignment Analysis 解决方案。

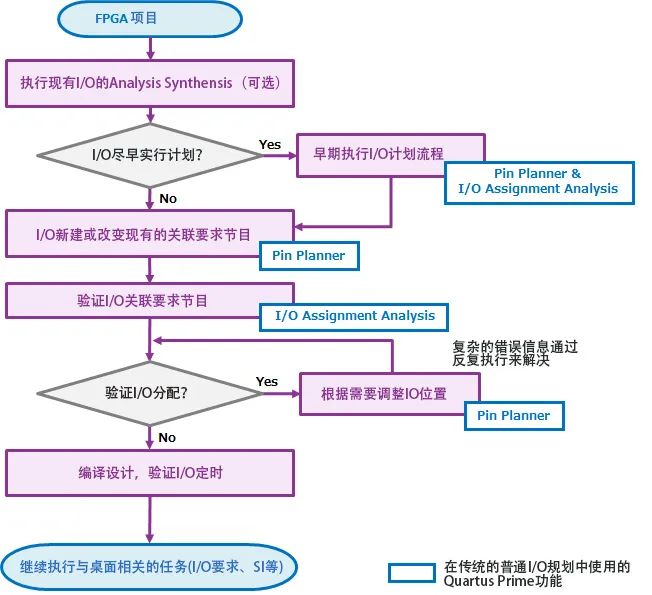

接下来创建 I/O 布局规划,在下图 (图1) 所示的工作流程中,将分别使用 Pin Planner 和 I/O Assignment Analysis。此流程使用 I/O Assignment Analysis 来分析引脚分配,I/O Assignment Analysis 的准确性取决于设计的完整性。如果检测到任何错误,需要在 Pin Planner 或其他工具中修复它们,并再次运行 I/O Assignment Analysis。如此循环往复,直到完成并验证所有 I/O 分配。

Altera 目前支持市场所需的多种协议,它还支持许多储存器接口,每个接口都有自己的放置规则。设计包含的接口越多,规则和限制就越复杂。即使工程师认为自己已经正确地放置了一个设计接口,但只有在完全编译期间运行 Fitter 或 I/O 分配分析时,才能知道它是否真的正确。如果一个元素因被放置在无效位置而导致不符合要求,则完全编译所花费的时间就会被浪费。

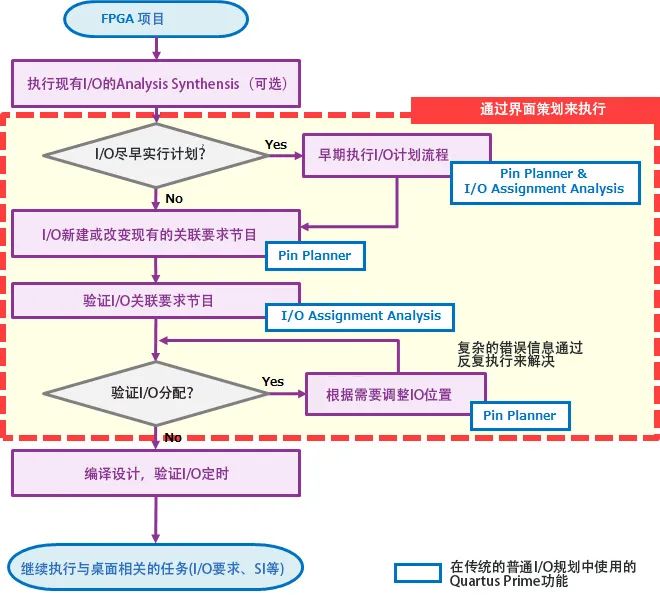

图1 传统 I/O 规划流程,I/O 布局规划工作流程,Quartus Prime Pro Edition Interface Planner 是一款引脚布局工具,可根据引脚布局规则以图形方式创建和实时验证复杂的 I/O 接口分配。下图 (图2) 显示了使用 Interface Planner 时的 I/O 布局规划工作流程。

图2 使用 Interface Planner 的 I/O 规划流程,Interface Planner 使用 Fitter 实时验证引脚分配,因此虽然需要预先进行逻辑综合 (Synthesis),但设计不需要完美无缺。要将界面设计分配给设备的资源,只需拖放或双击平面图即可。创建的分配计划将以 TCL 脚本的形式生成并执行,并在反映项目后进行编译。

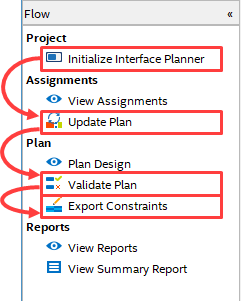

I/O 布局规划工作详细步骤,接下来将介绍 Interface Planner 的工作流程详细步骤,如下图 (图3) 所示。请注意,此时用户应已完成引脚分配。

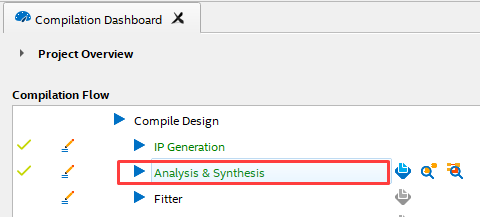

图3 Interface Planner 工作流程,一、综合设计,在 Quartus Prime Pro Edition (以下简称 Quartus Prime) 中,从 Processing 菜单或 Compilation Dashboard 运行 Analysis & Synthesis,如下图 (图4) 所示>

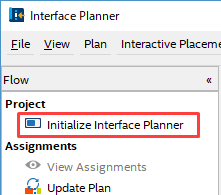

图4 运行分析与综合,二、启动并初始化 Interface Planner,点击 Tools 菜单,启动 Interface Planner。单击下图 (图5) 所示 Flow 窗格中的 Initialize Interface Planner 以检查 Fitter 基础和现有位置分配的有效性。如果存在冲突或违规,错误消息将显示在控制台窗格中。

图5 Initialize Interface Planner,三、检查导入的任务并更新计划,单击 Flow 窗格中的 View Assignments。Assignments 选项卡将变为活动状态并列出项目中存在的所有分配,如下图 (图6) 所示。接下来单击 Flow 窗格中的 Update Plan,已启用配置的分配将应用于设计以进行规则检查。

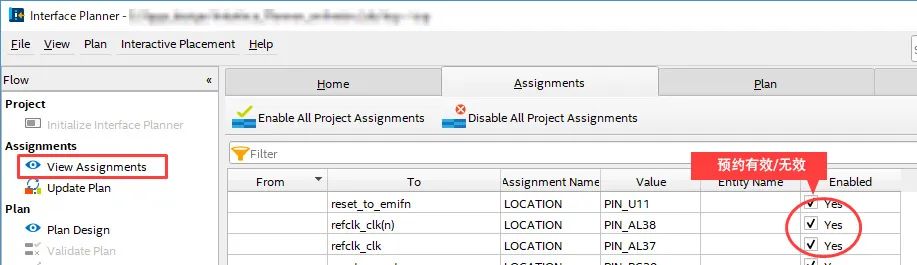

图6 View Assignments,四、放置设计元素,如下图 (图7) 所示,单击 Flow 窗格中的 Plan Design (Plan 选项卡变为活动状态)。

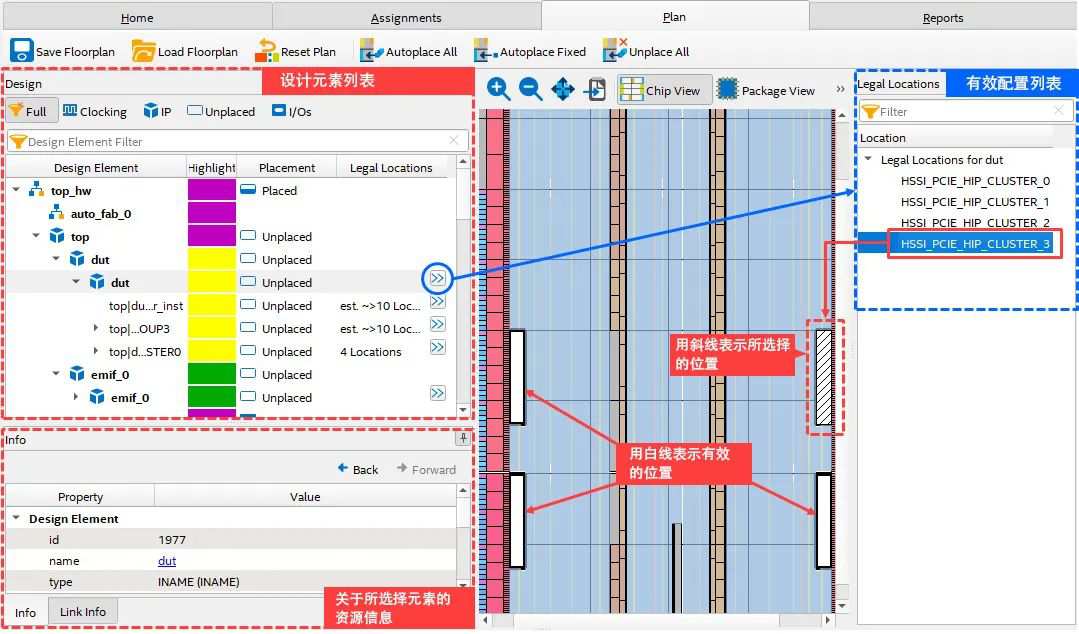

图7 Plan Design,如果单击 Design 窗格中未分配的设计元素右侧的按钮,Legal Locations 窗格中将显示可分配位置的列表,并且该位置将在 Chip View 中以轮廓显示。当从 Legal Locations 窗格中指定放置位置时,Chip View 显示将变成一条对角线。要确认分配位置,请双击下图 (图8) Legal Locations 窗格中的位置信息。

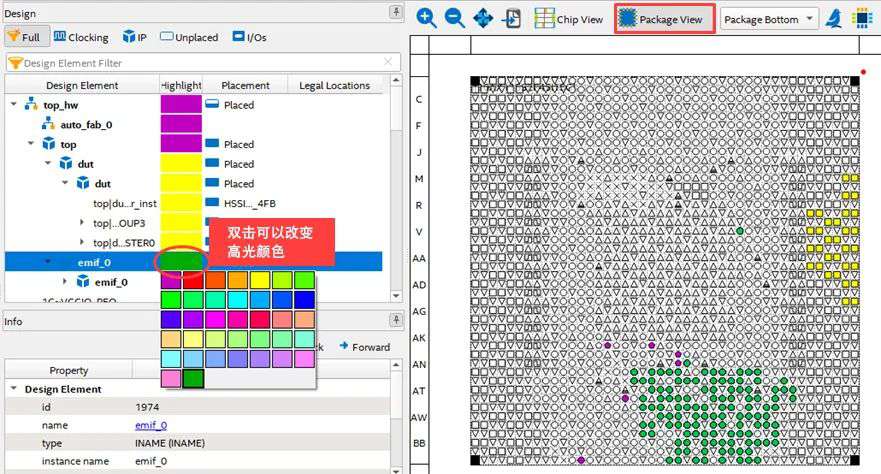

图8 确认位置 (Legal Locations 窗格),大家还可以切换到如下图 (图9) 所示的 Package View 以查看接口中使用的 I/O 引脚,也可以截取计划的屏幕截图,以便稍后将其与编译的设计进行比较。

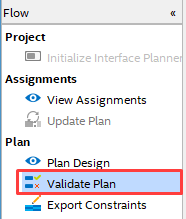

图9 Package View,五、验证 I/O 计划,完成放置规范后,单击下图 (图10) Flow 窗格中的 Validate Plan,这将验证已创建的任务并使其准备好导出。

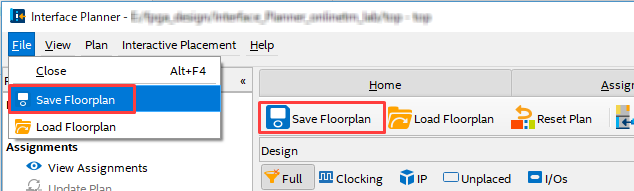

图10 Validate Plan,也可以通过选择下图 (图11) 中的 Save Floorplan 来保存当前的布局设置>

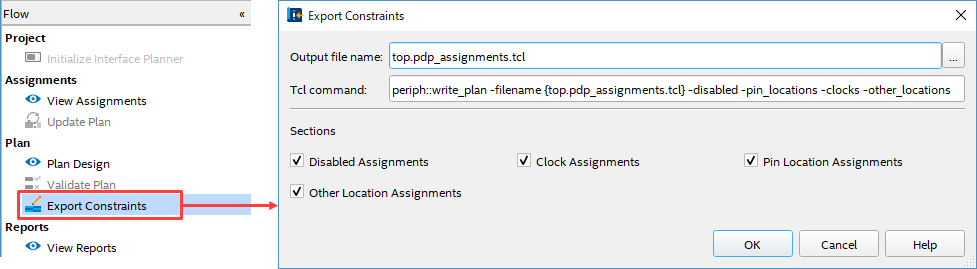

图11 Save Floorplan,六、导出计划文件,如下图 (图12) 所示,单击 Flow 窗格中的 Export Constraints 并使用 tcl 脚本保存配置的放置信息>

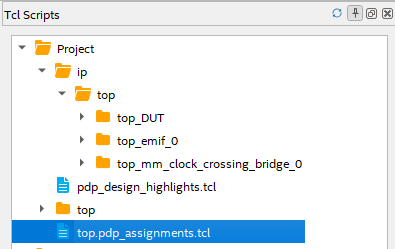

图12 Export Constraints,七、导入工程并编译,关闭 Interface Planner 并打开要导入的 Quartus Prime 项目。从 Tools 菜单 > Tcl Script,如下图 (图13) 所示,指定导出的 tcl 文件,然后单击 Run 以应用它。分配信息反映在 Pin Planner 和 Assignment Editor 中,可以轻松查看和最终检查脚本信息。在运行脚本之前可以使用 Edit 按钮对其进行编辑。例如 Interface Planner 不会在设计中导出所有的分配类型,如果只想进行引脚分配而不是内部资源分配,则可以通过注释或删除它们,从而仅提供脚本的引脚分配部分。

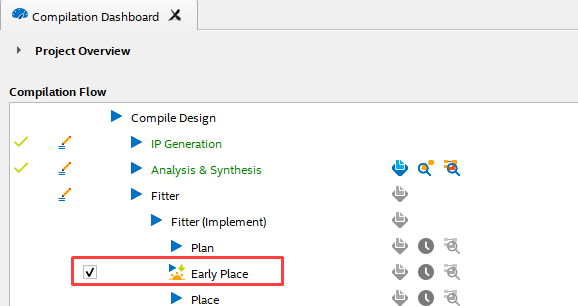

图13 Tcl Script,接下来运行编译。由于 Analysis & Synthesis 阶段到 Fitter (Finalize) 阶段需要很长时间才能运行,如果只想评估布局,可以在下图 (图14) 的 Compile Dashboard 中启用 Early Place 选项并执行 Early Place 编译。

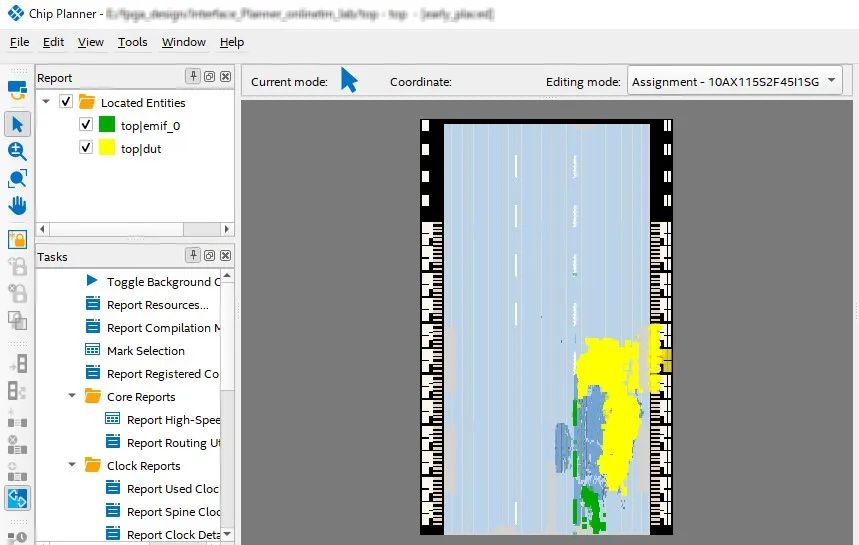

图14 Early Place,编译完成后,启动 Chip Planner (Tools 菜单) 并检查布局,如下图 (图15) 所示>

图15 启动 Chip Planner,总结,Quartus Prime Pro Edition 的 Interface Planner 消除了为 FPGA 创建专业规划的工作量和难度,特别是日益多样化和复杂 I/O 接口,它可允许仅创建有效的位置分配。通过使用 Altera Interface Planner,可以减少进行位置分配所花费的时间。